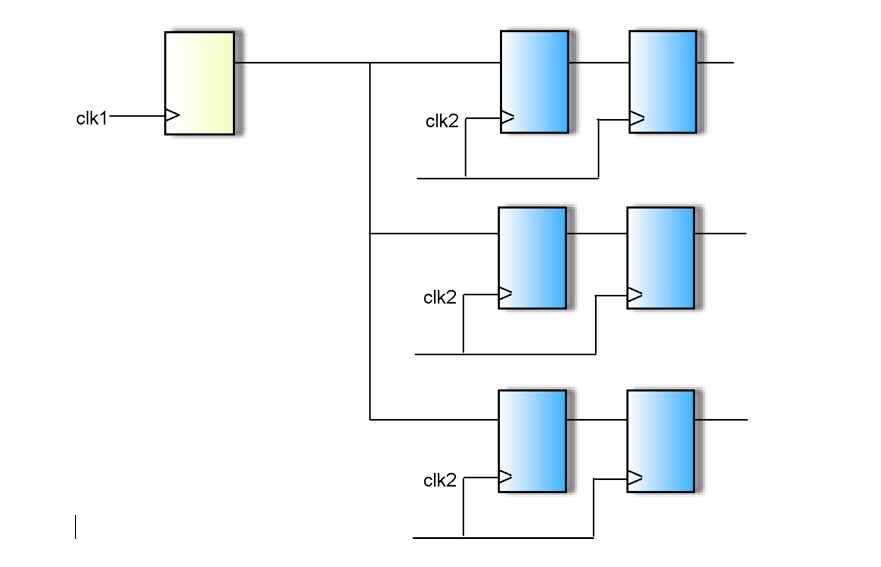

The idea here is that by keeping 2 FF in the destination clock domain, the signal has enough time for the meta-stability to settle down. clock domain crossing (CDC) is on a control signal (either single bit or multibit).īy satisfying this criteria we can be sure that the destination clock captures any possible changes in signal without loss.the source clock domain is slower than destination clock domain.This Technique can be used if the following criteria is satisfied. Using Xilinx specific clock domain crossing (CDC) tools.Using FIFOs (First In First Out memories).Here a meta-stable condition could cause the design to activate wrong data-paths or move the design to an invalid state.Ĭommon methods for synchronizing data between clock domains are: In FPGA latching a meta-stable signal can cause entire designs to come to halt.įor example let us consider a case statement If a signal is passed between two clock domains then there is a chance that the signal could go meta stable, i.e a state where the signal is has not settled to either a high or low (1 or 0). But, 100MHz and 59MHz clocks (whose phase relationship changes over time) are in two separate clock domains. For example, a clock and its derived clock (via a BUFR, Divider) are in the same clock domain because they have a constant phase relationship. This Section covers the following topics:Ī clock domain is a part of a design that has a clock that operates on a single clock and is often asynchronous to, or has a variable phase relationship with, another clock in the design. CDC Synchronization Techniques – Discusses the synchronization techniquesįPGA Clock Domain Crossing (CDC) Background.Background – Prepares the background required for further discussions.This document is organized into the following sections: Improper clock domain crossing can cause the design to stop working at random times and hence can be disastrous if left unchecked. This document provides an overview of the importance of clock domain crossing (CDC) and introduces the reader to methods and techniques for taking care of clock domain crossing so that the design meets all functional requirements for a stable design.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed